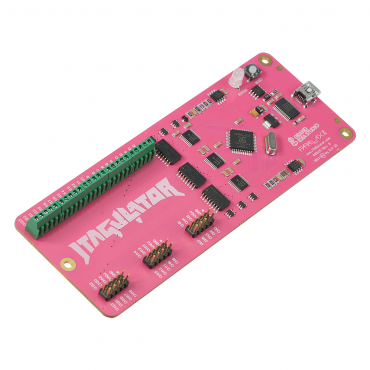

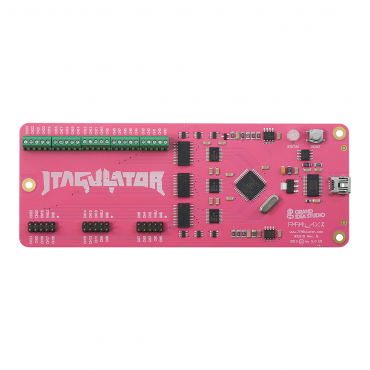

JTAGulator

Product Code: JTAGulator-01_32115

Weight:0.50 lb

Reward Points:0

| Video footage | |||

|

- Grand Idea Studio JTAGulator product page (Product brief, schematics, bill-of-materials, assembly drawing, etc.).

- JTAGulator: Assisted Discovery of On-Chip Debug Interfaces slide presentation.

- JTAGulator source code repository.

- EEVblog #499: What is JTAG and Boundary Scan.

- Joe Grand's JTAGulator presentation at DerbyCon 2013.

- What is OpenOCD?

- OpenOCD User’s Guide.

- What is JTAG and why use it?

On-chip debug (OCD) interfaces can provide chip-level control of a target device and are a primary vector used by engineers, researchers, and hackers to extract program code or data, modify memory contents, or affect device operation on-the-fly. Depending on the complexity of the target device, manually locating available OCD connections can be a difficult and time consuming task, sometimes requiring physical destruction or modification of the device.

Designed by Grand Idea Studio, JTAGulator is an open source hardware tool that assists in identifying OCD connections from test points, vias, or component pads on a target device.

Key Features:

- 24 I/O channels with input protection circuitry.

- Adjustable target voltage: 1.2 V to 3.3 V.

- Supported target interfaces (as of firmware v1.1): JTAG/IEEE 1149.1, UART/asynchronous serial.

- USB interface for direct connection to host computer (PC, Macintosh, or *nix).

Application Ideas:

- Discover on-chip debug interfaces.

- Simple logic analyzer.

- Propeller development board.

NOTES: Proper use of this tool requires basic electronics knowledge. To avoid damage to the JTAGulator or target circuitry, please take care to ensure the proper target voltage level is set. Some on-chip debug interfaces may not be detectable if password protection or other security mechanisms are implemented.